# SynaptiCAD WaveFormer Pro

Verilogger Pro/ TestBencher Pro

## Interactive Verilog Simulator の概要と操作

Verilogger Pro/TestBencher Pro にも共通!!

## What is WaveFormer Pro?

- タイミング・ダイヤグラムの編集と スタティック・タイミングアナライザでの解析

- スティミュラスの生成とシミュレータ、ATEのI/Fをサポート VHDL、Verilog、ABEL、Minc、ViewLogic、Mentor、 Altera、Aldec-Xilinx、Spice . . . . . VCD(Verilog ) HPロジックアナライザ、STIL IEEEテスター・フォーマット TDML標準化タイミング記述フォーマット(SI2-ECIX) !! インターフェース仕様公開でPerl言語で追加/カスタマイズ可能!!

- ・インターラクティブVerilog-HDLシミュレータ

- ・マウス操作で入力された波形やRTL論理式から Verilog設計 コードを自動生成

- ・変更毎に再シミュレーションが自動実行

- ・入力と確認が同時のためRTL設計入力の効率化

- ・ Verilogコードの直接入力とインクルード可能

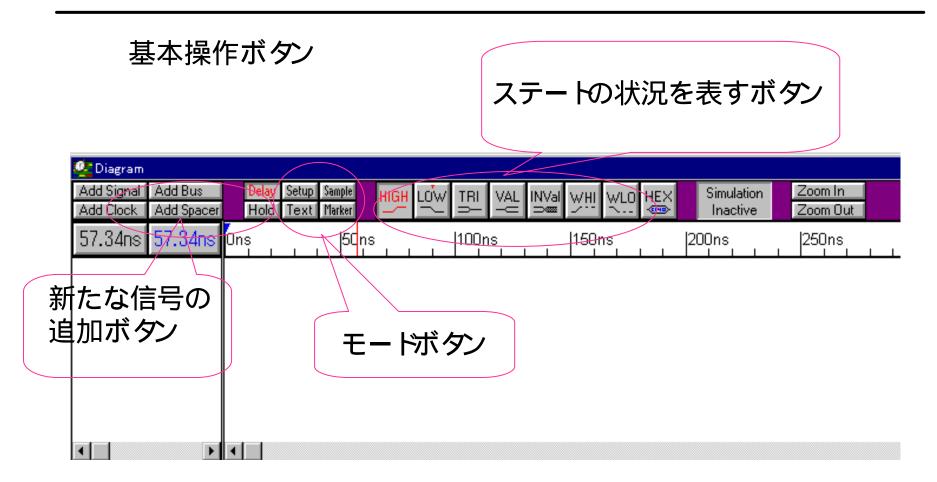

#### WaveFormer Pro 超!簡単な基本操作(1)

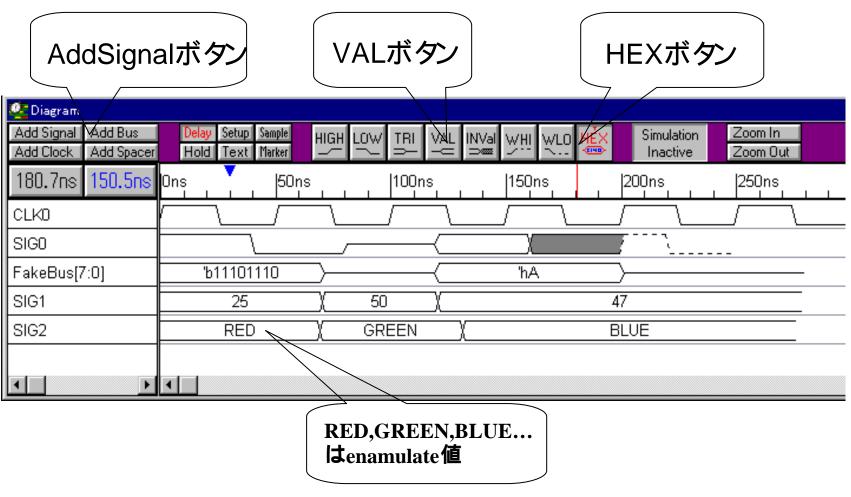

主な操作は、上記のアイコンで実行できます。

#### WaveFormer Pro 超!簡単な基本操作(2)

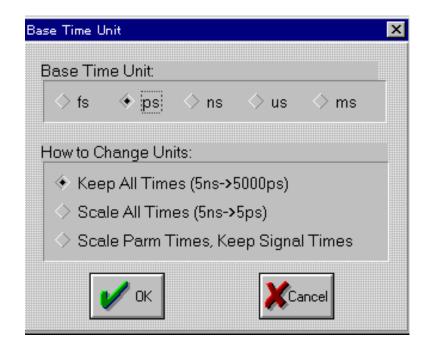

基本時間単位設定

表示時間単位設定

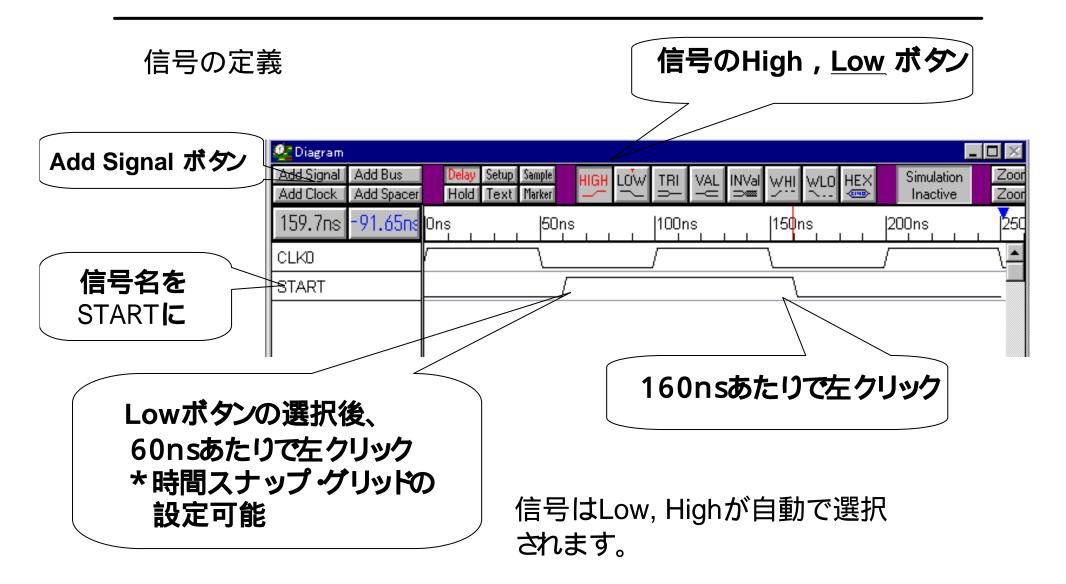

信号の定義/追加

信号の属性を決定

基本時間単位設定 ダイアログ・ボックス

#### WaveFormer Pro 超!簡単な基本操作(3)

🔑 Diagram

Add Signal | Add Bus

Add Spacer

Text

clockの定義は、

OKを押します。

Add Clock ボタンを押す

すると このようにデフォルトで cbck0の波形ができ、 Edit Clock Propaties ダイアログ が表れます。 デフォル H値を確認して、必要なら変更し

通常の信号」も パス」もマウス・クリックまたは簡単な式で素早く入力可能

**X**Cancel

TRI VAL INVal WHI WLO HEX

#### WaveFormer Pro 超!簡単な基本操作(4)

#### WaveFormer Pro 超!簡単な基本操作(5)

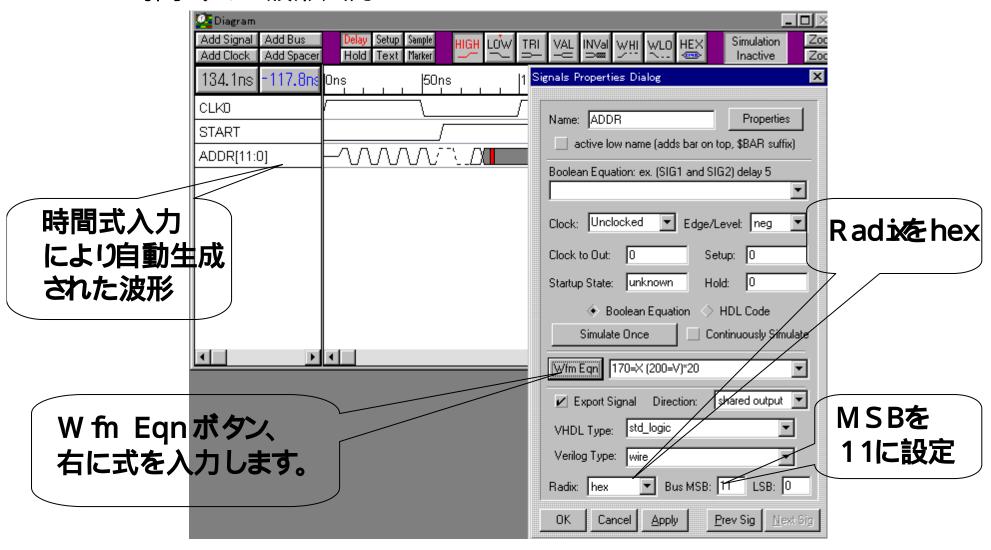

#### 時間式での波形入力

#### WaveFormer Pro 超!簡単な基本操作(6)

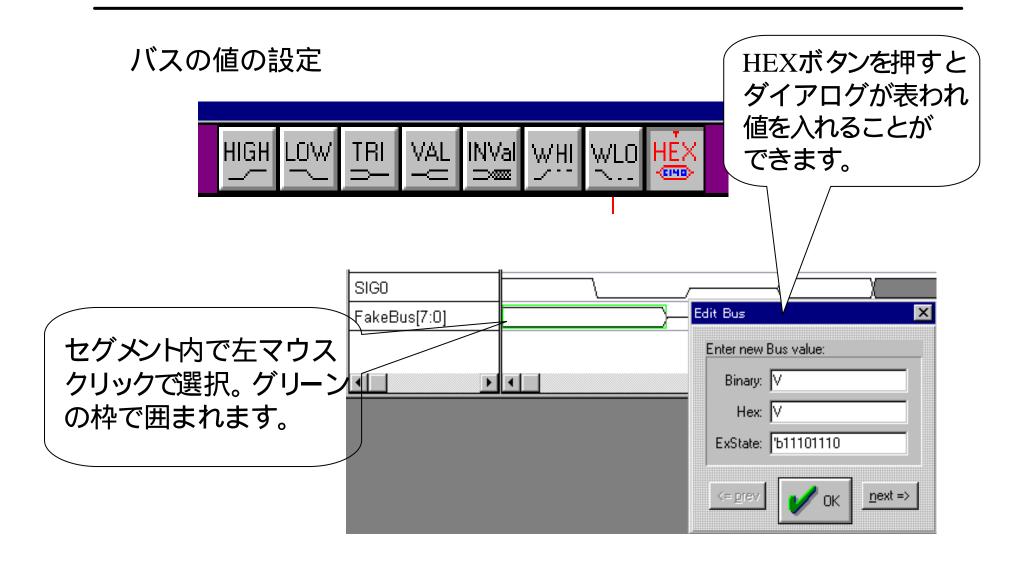

#### WaveFormer Pro 超!簡単な基本操作(7)

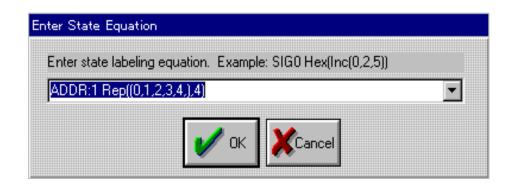

-1 バスの値 (ステート名)の入力の自動化

-2 上記定義で下記のように波形が描けます。

#### WaveFormer Pro 超!簡単な基本操作(8)

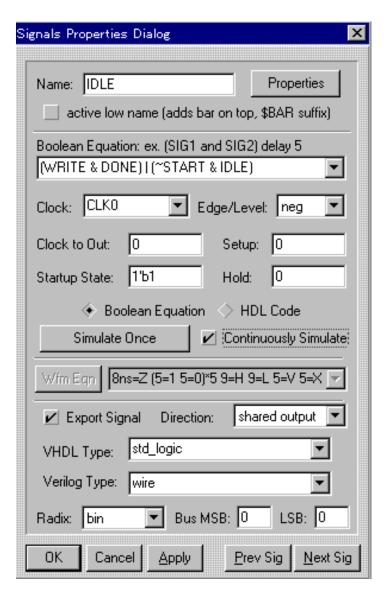

## RTL <sub>設計入力</sub>

ブーリアン論理式を他の信号へ代入

- \* 組み合わせ論理として

- \* レジスタへ

- !! WaveFormer が Verilogコードに変換し

- !! VeriWellで自動シミュレーション

(注)HDLコード入力ダイアログに直接に Verilogコードを入力することも可能

#### WaveFormer Pro 超!簡単な基本操作(9)

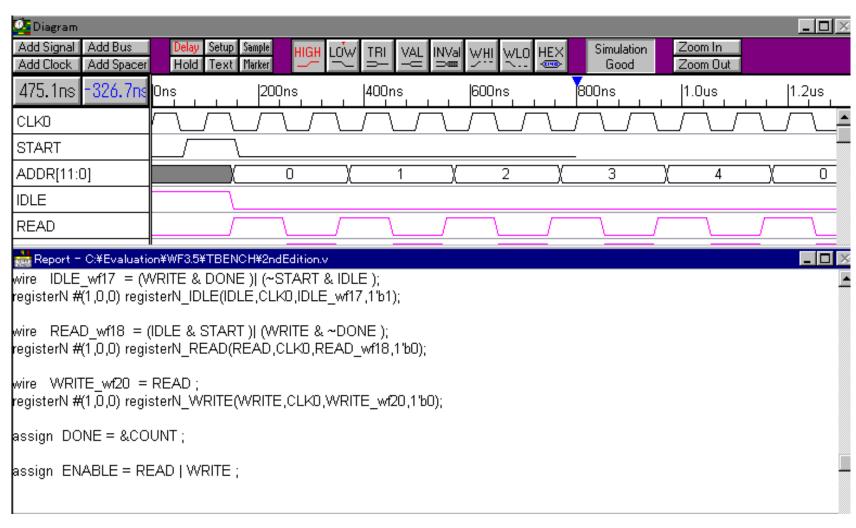

WaveFormerにより 生成されたVerilog コー

充実したエラーログも出力され、 効率的なデバッグが可能です。

```

TestBencher Pro = UNTITLED.TIM = [Report = C:¥Evaluation¥WF3.5¥TBENC

File Export Edit Draw Bus Libraries View Options Report

`timescale 1ns / 1ps

module top;

wire CLKO;

wire START;

wire [11:0] ADDR;

wire IDLE;

wire READ:

wire WRITE:

testbed tbed(

CLK0,START,ADDR,IDLE,READ,WRITE

initial

begin

$sdf annotate("C:/Evaluation/VVF3.5/TBENCH/UNTITLED.sdf");

#4170 $finish:

end

lendmodule

`include "wavelib.v"

module testbed(CLK0,START,ADDR,IDLE,READ,WRITE);

output CLKO;

```

#### スティミュラスの自動生成 Verilog コード(1)

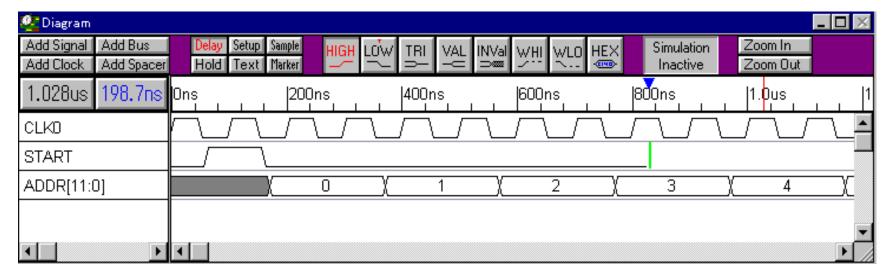

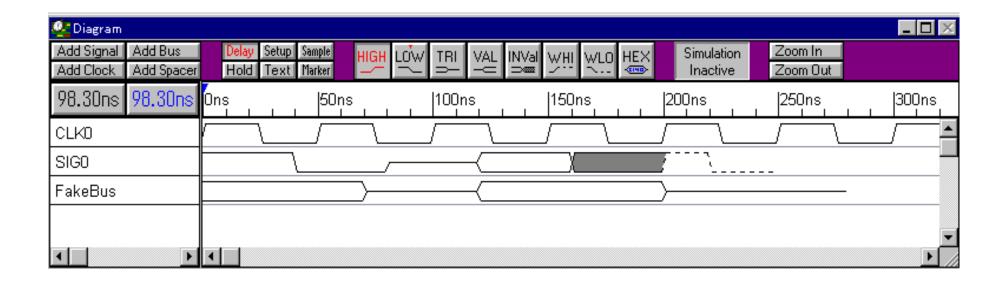

下記3つの信号によりVerilogスティミュラスの生成例を見てみましょう。

CLK0: 一周期 50nsのクロック

SIG0: WaveFormerで扱える全ての波形ステートを持った信号

FakeBus: トライステートセグメントを持った仮想バス信号

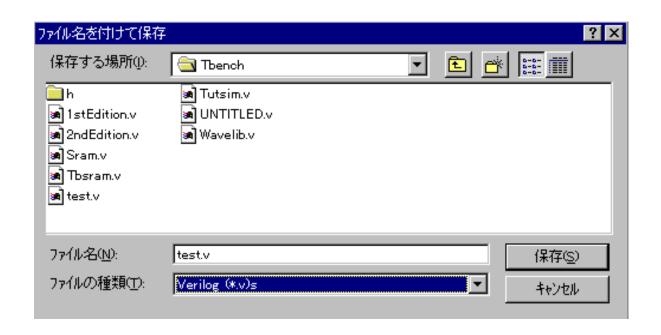

## スティミュラスの自動生成 Verilog コード(2)

-1 Verilog-HDL コードの生成

-2 では実際に生成されたテストベンチファイルを見てみましょう

## スティミュラスの自動生成 Verilog コード(3)

生成されたVerilog コードのテストベンチ

```

🎬 test.v - 妊帳

ファイル(F) 編集(E) 検索(S) ^ルプ(H)

`timescale 1ps / 1ps

|module testbed(CLK0,SIG0,FakeBus);

loutput CLKO;

reg CLKO;

loutput SIGO;

reg SIGO;

|output [7:0] FakeBus;

reg [7:0] FakeBus;

integer CLKO_stop_time;

integer CLKO_period, CLKO_duty,CLKO_offset;

integer CLKO_d1, CLKO_d2;

initial

ZZCLOCK CLKO

begin

CLK0_stop_time = 280576;

CLKO_offset = 0;

------ 中 略 ------

linitial

//SIGNAL FakeBus

begin

FakeBus = 8'b11101110:

#70000

FakeBus = 8'bzzzzzzzz;

#50000

FakeBus = 8'b00001010;

#80000

FakeBus = 8'bzzzzzzzz:

#80576

```

## スティミュラスの自動生成 Verilogコード(4)

#### WaveFormerの大きな特長

システムのインターフェース は全てPerl言語で記述され、 WaveFormer Pro本体との プロトコル仕様が公開されて おり、カスタマイズ可能 (例)

Verilogスティミュラスを生成する Verilog.epl ファイルを見てみましょう

```

III Verilog.epl − 灹帳

^ルプ(<u>H</u>)

🖟 Copyright 1996 SynaptiCAD

# Requires TWF v3.0 or greater

Export to Verilog

#(strict compliant)

|$|=1;

l#uses "future state" format

require 'twfsubs.pl';

|%ToState = ('1' => '1',

=> 'weak1',

_' => 'weak0',

IF_To_Verilog();

return 1;

|sub_IF_To_Verilog {

$LastOutputTime = twf::GetLastOutputTime();

$BUnits = $twf::ToUnits[ twf::GetOptions()->GetBaseTimeUnit() ];

$DUnits = $twf::ToUnits[ twf::GetOptions()->GetBaseTimeUnit() ];

print "`timescale 1$DUnits / 1$BUnits\n";

```

#### スティミュラスの自動生成 VHDL コード(1)

#### VHDLでは直接値入力以外に enamulation をサポート

InterLink June, 1999

#### スティミュラスの自動生成 VHDL コード(2)

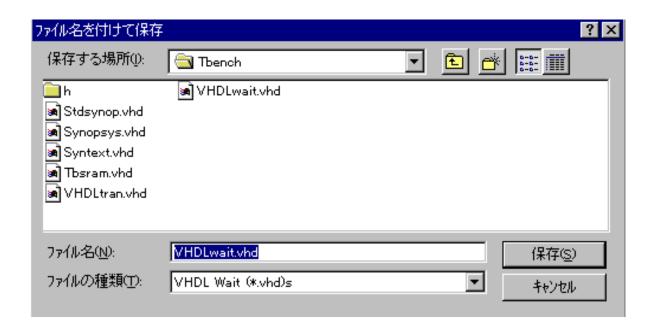

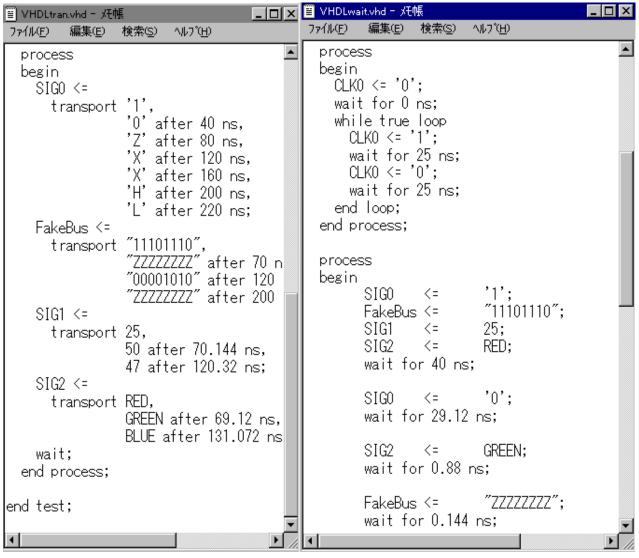

VHDLtran.vhd とVHDLwait.vhd を作成します。

#### スティミュラスの自動生成 VHDL コード(3)

#### VHDLtran.vhd

#### VHDLwait.vhd

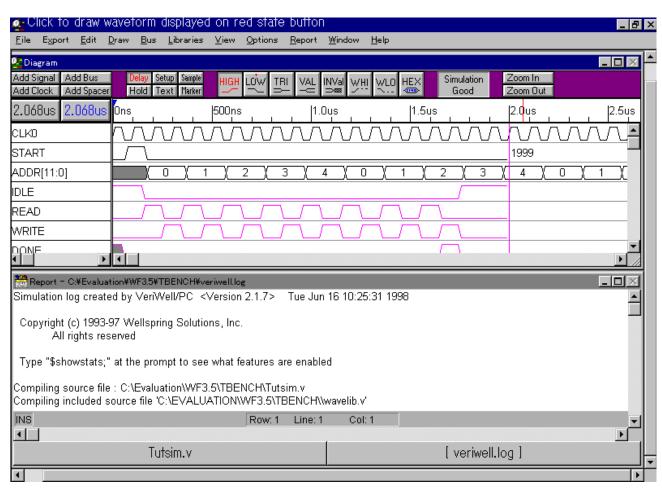

#### WaveFormer Pro インターラクティブ・シミュレータ(1)

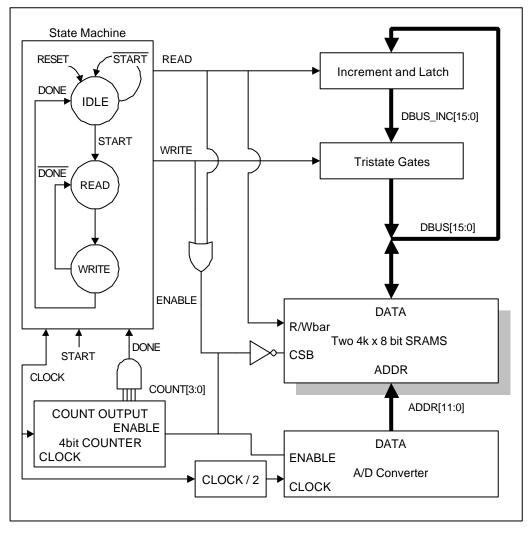

この程度の中規模の設計であれば RTL入力機能で素早くモデル化可能

InterLink June, 1999

#### WaveFormer Pro インターラクティブ・シミュレータ(2)

前ページのモデル=シミュレーション波形とVerilogコードの同時出力